지난날 반도체는 수평으로 배치됐다. 현재 상보형 금속 산화 반도체(CMOS) 공정 기반 칩이 단층의 수평 평면에 트랜지스터를 배치하는 데 최적화됐기 때문이다. 또, 전류가 흐를 때도 수평 배치된 금속 배선이 더 짧고 균일하게 설계 가능하다는 점도 반도체가 수평 배치되던 이유다.

그러나 오늘날 수평 배치는 집적도의 한계에 부딪혔다. 동일한 평면 위에 넣을 수 있는 트랜지스터 수에 물리적 제한이 걸린 탓이다.

삼성전자가 업계 최초로 개발한 8세대 V낸드 기반 차량용 SSD(사진=삼성전자)

3D 반도체, 평면의 끝에서 시작된 입체 전쟁

이에 반도체 업계에서 주목하는 기술이 3D 반도체다. 3D 반도체는 칩을 쌓아올린 기술이다. 기존 평면(2D) 반도체보다 집적도와 성능이 향상되면서도 전력 효율이 좋다. 3D 기술은 D램, 낸드플래시, SoC(시스템 온 칩) 등 다양한 반도체에 적용될 전망이다.

국내외 기업의 경우 제조업체를 중심으로 3D 반도체 개발에 한창이다.

삼성전자는 로직(시스템 반도체), 메모리, 패키징 전 영역에서 3D 반도체를 구현하려는 유일한 기업이다. 특히 3나노 이하 로직 반도체에 세계 최초로 적용한 GAA(게이트 올 어라운드) 기술에 3D 구조를 적용한다. GAA는 트랜지스터 핵심 구성요소인 채널 4개면을 게이트가 둘러싼 형태로, 기존 3개면이 접합된 핀펫(FinFET) 대비 고성능·저전력 반도체를 쉽게 구현할 수 있다. 삼성전자가 현재 연구 중인 3D GAA 구조는 ‘3DSFET’으로 불리며, 3D 적층과 GAA를 결합하고 있다.

SK하이닉스의 경우 최근 실적을 견인하고 있는 HBM(고대역폭 메모리)이 D램 다이를 적층하고 TSV(실리콘 관통전극)로 연결한 3D 메모리다. 시장 1위인 HBM 기술력을 앞세워 단순 D램, 낸드 등 메모리 제조에서 벗어나, AI·고성능 연산에 적합한 프리미엄 메모리 중심의 기술 리더십 확보에 집중하고 있다.

TSMC는 세계 1위 파운드리 기업답게, 3D 패키징과 칩렛 아키텍처에서 독보적인 경쟁력을 보여주고 있다. SoIC(system on Integrated Chips)이 TSMC의 대표적인 수직 적층 3D 기술이다. SoIC는 다양한 기능의 칩을 수직 방향으로 연결해 성능을 높이고 전력 손실을 줄이는 기술로 애플, AMD, 브로드컴 등 글로벌 기업들이 SoIC 기술을 활용하고 있다.

아울러 TSMC는 공정 미세화와 3D 패키징 결합을 통해 파운드리 경쟁력을 유지하며, 고부가가치 설계 기업들과의 파트너십을 적극 강화 중이다.

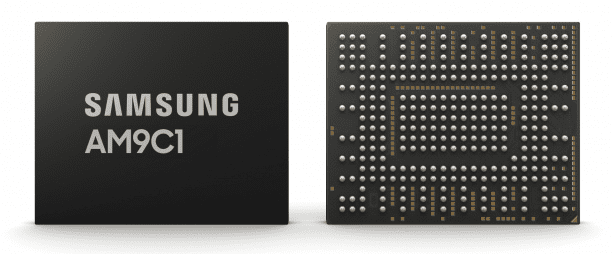

램리서치의 극저온 식각 기술인 Lam Cryo™ 3.0은 업계 최고의 정밀도와 제어로 머리카락 지름의 1/1000에 불과한 작은 피처를 식각하는 획기적인 기술이다. (사진=램리서치)

3D 반도체 핵심 기술 ‘극저온 식각’

이를 위해 필요한 기술이 바로 ‘극저온 식각’ 기술이다. 식각은 반도체 웨이퍼 표면을 원하는 패턴대로 깎아내는 공정으로, 극저온 식각은 영하 60~70°C 환경에서 식각을 진행한다. 기존 식각 대비 30~40°C 가량이 더 낮은 환경에서 식각을 진행하는 것이다.

이처럼 낮은 온도에서 극저온 식각을 진행하는 이유는 정밀한 식각이 가능하기 때문이다. 해당 기술이 적용될 때 플라즈마는 실리콘 표면을 화학적으로 반응해 깎아낸다. 이후 산소가 산화막을 형성해, 저온 상태에서 고체 보호막으로 표면에 남는다. 이 보호막이 식각 방향성을 제어하며 옆면이 깎이지 않도록 보호하는 것이다. 보호막은 식각 후 온도를 올리거나 플라즈마로 제거한다.

관련기사

- 민주당, 김홍일 방통위원장 탄핵 추진..."6월내 통과 목표"2024.06.27

- 김홍일 위원장 "2인 체제 방통위, 바람직하지 않지만 위법 아니다”2024.06.21

- LG 구광모 6년...AI·바이오·클린테크 키운다2024.06.28

- 화재 막는 배터리 진단기술 뜬다...민테크, 상장 후 존재감 '쑥쑥'2024.06.28