삼성전자가 첨단 패키징 기술로 IBM과의 협력을 강화한다. IBM이 최근 출시한 차세대 프로세서에 3D 적층 기술을 성공적으로 양산 공급한 것으로 파악됐다.

27일 업계에 따르면 IBM은 삼성전자 7나노미터(nm) 공정 및 3D 패키징을 적용한 'Power11(P11)' 칩을 이달 공식 출시했다.

P11은 IBM의 자체 아키텍처를 기반으로 한 서버용 CPU다. 654mm² 면적에 총 300억개의 트랜지스터를 집적했다. 이전 세대인 P10 대비 클럭 속도가 향상됐으며, 프로세서 당 최대 25% 더 많은 코어를 추가할 수 있도록 설계됐다.

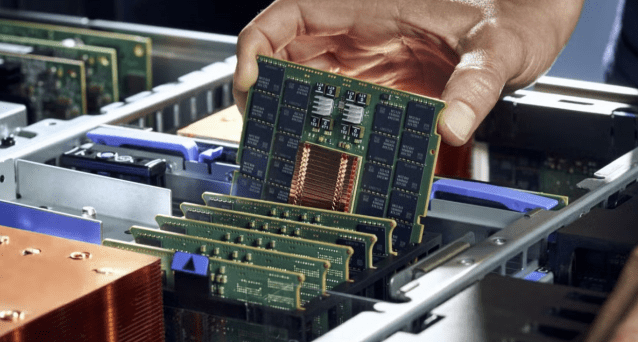

IBM의 P11 프로세서와 메모리 모듈이 결합된 보드(사진=IBM)

IBM 자료에 따르면 P11은 삼성전자 파운드리 7나노 공정을 채택했다. 이전 P10과 같은 공정이지만, 삼성전자의 3D 패키징 기술을 통해 'ISC(Integrated Stack Capacitor; 통합형 적층 커패시터)'를 도입해 차별점을 뒀다.

커패시터는 전하를 일시적으로 저장할 수 있는 전자부품이다. 회로에 전류가 일정하게 흐르도록 조절하고 부품 간 전자파 간섭현상을 막아준다.

기존 커패시터는 PCB(인쇄회로기판)나 첨단 패키징에서 중간 기판 역할을 담당하는 인터포저 위에 부착돼 왔다. 반면 ISC는 커패시터를 패키지 내부로 끌어들여, 칩 아래에 직접 배치한다. 커패시터와 칩간 거리가 가까워지면서 더 많은 전력을 빠르게, 그리고 안정적으로 보낼 수 있게 된다.

삼성전자는 ISC를 3D 패키징을 통해 집적했다. 웨이퍼 상에 ISC를 만들고 그 위에 IBM의 프로세서를 올린 뒤, TSV(실리콘관통전극)로 연결해 TC(열압착) 본딩을 진행하는 방식이다. IBM은 이를 2.5D 패키징으로 기술했으나, 삼성전자는 ISC와 칩을 수직 적층했다는 점에서 3D 패키징으로 정의하고 있는 것으로 알려졌다.

관련기사

- 민주당, 김홍일 방통위원장 탄핵 추진..."6월내 통과 목표"2024.06.27

- 김홍일 위원장 "2인 체제 방통위, 바람직하지 않지만 위법 아니다”2024.06.21

- LG 구광모 6년...AI·바이오·클린테크 키운다2024.06.28

- 화재 막는 배터리 진단기술 뜬다...민테크, 상장 후 존재감 '쑥쑥'2024.06.28